## Using *dq*-rotating reference frame in single phase system – Digital implementation

This report presents how to use *dq-rotating* reference frame in single phase system. The *dq-rotating* reference frame is mainly used in three-phase systems due to AC signals in *abc* frame be represented as DC singal in *dq*. Therefore, the controller design is simplified. The application of *dq* frame in single phase system is known in the literature.

The simulation file (PSIM) with automatic code generation used in this report is freely available on <u>https://sites.google.com/site/busarellosmartgrid/material-didatico-didactic-material/dq-</u> <u>rotating%20reference%20frame%20in%20single%20phase%20system%20%E2%80%93%20Digital%20impleme</u> <u>ntation.psimsch?attredirects=0&d=1</u>

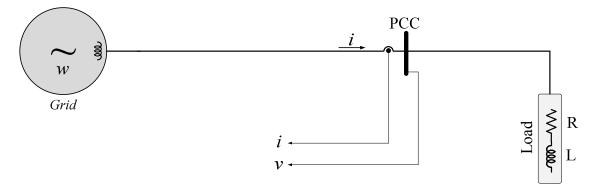

Fig. 1 presents the single-phase system showing the measured variables. The load is a RL.

Fig. 1. Single-Phase system showing the measured variables.

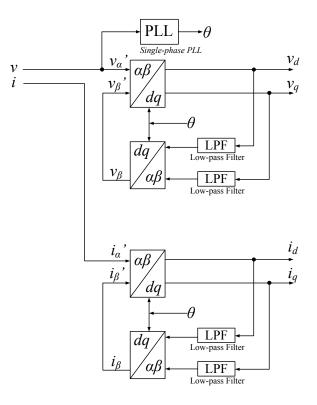

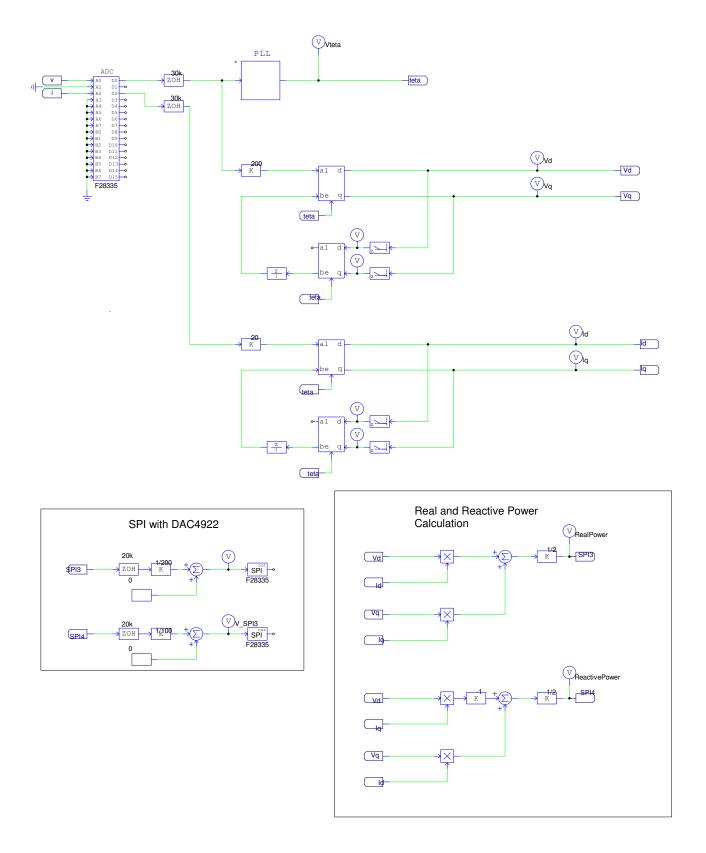

Fig. 2 presents how to use *dq-rotating* reference frame in single phase system. A Phase-Locked Loop (PLL) is required to make the *dq-rotating* frame rotating. In this case, the *dq* transformation rotates at the grid frequency (60Hz). The voltage and current are transformed to *dq* quantities  $v_{dr}$   $v_{qr}$   $i_d$  and  $i_{qr}$ .

Fig. 2. How to use *dq-rotating* reference frame in single phase system.

## **Experimental Results**

The  $\alpha\beta$  to dq transformation is given by (1).

$$\begin{bmatrix} v_d \\ v_q \end{bmatrix} = \begin{pmatrix} \cos(\theta) & \sin(\theta) \\ -\sin(\theta) & \cos(\theta) \end{bmatrix} \begin{bmatrix} v_\alpha \\ v_\beta \end{bmatrix}$$

(1)

And the dq to  $\alpha\beta$  transformation is given by (2).

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = \begin{pmatrix} \cos(\theta) & -\sin(\theta) \\ \sin(\theta) & \cos(\theta) \end{pmatrix} \begin{bmatrix} v_{d} \\ v_{q} \end{bmatrix}$$

(2)

The angle  $\theta$  in the above-mentioned equations is supplied by the PLL. From these equations and in order to have the *d* axis aligned to the voltage phase, the PLL should be synchronized according to the following figure.

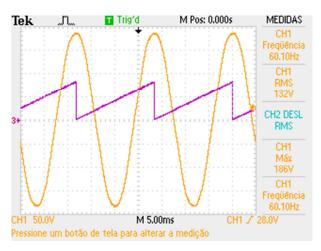

Fig. 3. The PLL should be syncrhonized at 90 degree in the voltage phase. Orange curve: grid voltage; Purple: PLL output signal  $\theta$ .

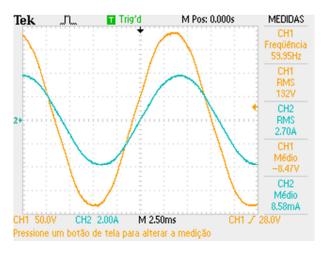

Fig. 4 shows the grid voltage and current. The grid voltage RMS is 132V (186V peak).

Fig. 4. Grid voltage (orange) and current.

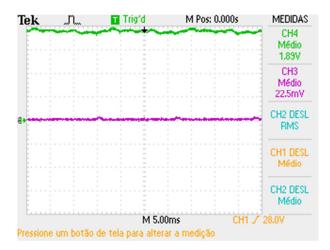

Fig. 5 presents the variables *vd* (channel 4) and *vq* (channel 3). These results were collected by means of the DAC4922 (Digital to analog converter). A scale factor equals to 1/100 was applied in both signals. Therefore, the channel 4 average valeu presented is equal to 189V (1.89 x 100). It corresponds to the grid peak votlage. The *vq* is zero, as expected.

Fig. 5. Variables vd (green, channel 4) and vq (channel 3).

The real power (P) and reactive power (Q) at the PCC in *dq-rotating* rotating reference frame is given by (3) and (4). Notice that the first term is  $\frac{1}{2}$  in single-phase system and  $\frac{3}{2}$  in three-phase system.

$$P = \left(\frac{1}{2}\right) \left(v_d i_d + v_q i_q\right) \tag{3}$$

$$Q = \left(\frac{1}{2}\right) \left(-v_d i_q + v_q i_d\right) \tag{4}$$

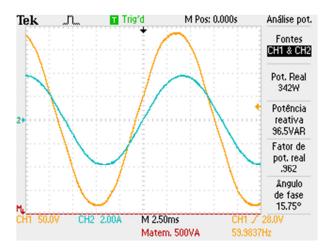

Fig. 6 presents the grid voltage and current with the measured real and reactive power. The real power is 342W and the reactive power is 96.5VAR. These powers were measured with the oscilloscope application key.

Fig. 6. Grid voltage and current with the measured real and reactive power.

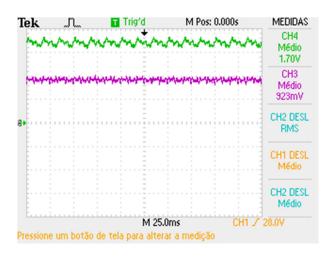

Fig. 7 presents the *P* and *Q* obtained by equations 3 and 4 and experimentally collected by means of the DAC4922. The channel 4 has a scale factor equals to 1/200 and channel 3 has 1/100. Therefore, the real power obtained by using equation 3 is equal to 340W. Similarly, the reactive power obtained by using equation 4 is equal to 92.3VAR. They are equal to those measured with the application key.

Fig. 7. Real power P (green, channel 4) and reactive power Q obtained by equations 3 and 4 and experimentally collected by means of the DAC4922.

Fig. 8 presents the simulated circuit.

Fig. 8. Simulated circuit.